To add value to our extensive portfolio of verification IP products, SmartDV has developed several automation tools that are designed to improve productivity and eliminate the need for tedious and error-prone manual effort. The tool suite is provided as a no-cost, value-added complement to our Verification IP customers.

The SmartDV automation tool suite includes SmartViPDebug™ and SmartTestBench™.

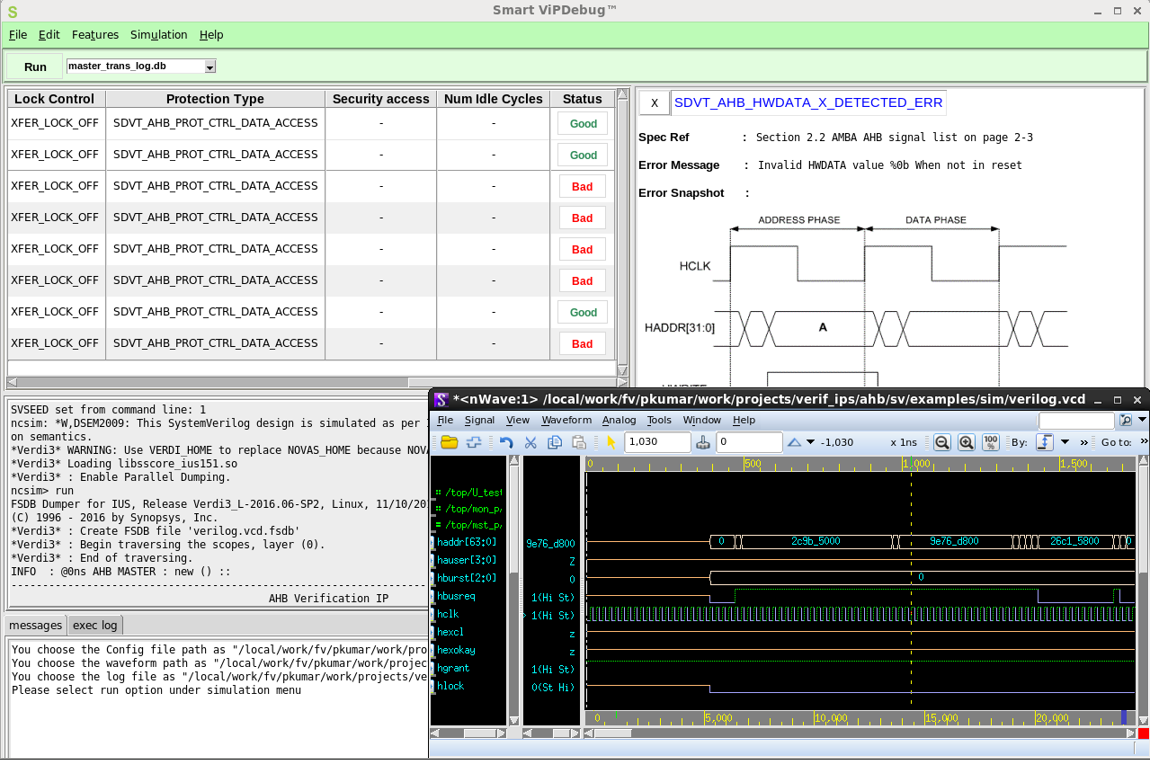

SmartViPDebug™

Detecting, debugging and fixing protocol violations is a critical part of the verification flow. Unfortunately, it is also time-consuming and typically requires detailed knowledge about the specific protocol being debugged.

SmartViPDebug employs visual and tabular views to simplify the identification of protocol violations by highlighting the violation in waveform view while also displaying a waveform showing the proper protocol behavior. This approach allows rapid troubleshooting of protocol violations without requiring the user to be an expert in the details of the specific protocol. SmartViPDebug works with all industry-standard waveform viewers.

SmartViPDebug utilizes a profile-based architecture that supports all industry-standard protocols. It is modular and scalable and extendable to make it easy to add custom or complex functionalities for debug. It supports multiple verification environments including simulation, emulation and SystemC.

View SmartViPDebug Datasheet >

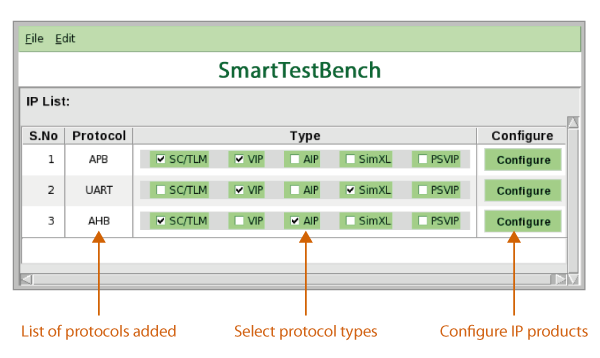

SmartTestBench™

Testbench creation is at the heart of developing a comprehensive verification program. However, creation of testbenches are often done manually resulting in tedious and time-consuming efforts.

SmartTestBench automates the creation of testbench files to support a wide variety of verification scenarios including:

— SystemC and Transaction-Level Modeling

— Verification IP in UVM, OVM, SystemVerilog and SystemC

— Assertion IP for use in Formal Property Verification

— SimXL, Synthesizable Transactor-based Acceleration for emulators and FPGA prototype

— Post-Silicon verification

SmartTestBench automates the process of testbench creation through an intuitive graphical user interface (GUI) or via text file. The GUI allows the user to visually add protocols, select the protocols and type of IP, and then configure the testbench for each protocol and IP type.

SmartTestBench also supports the testbench creation process via text file input. It is fully customizable to fit the user’s design configuration requirements for text file entry. Not only does this speed up the testbench creation process, it also creates a higher-quality testbench due to automation that eliminates manually-induced errors.

View SmartTestBench datasheet >